- 您现在的位置:买卖IC网 > Sheet目录477 > MICRF505DEV1 (Micrel Inc)KIT DEV RADIOWIRE 850-950MHZ

�� �

�

�

�Micrel�

�Programming�

�General�

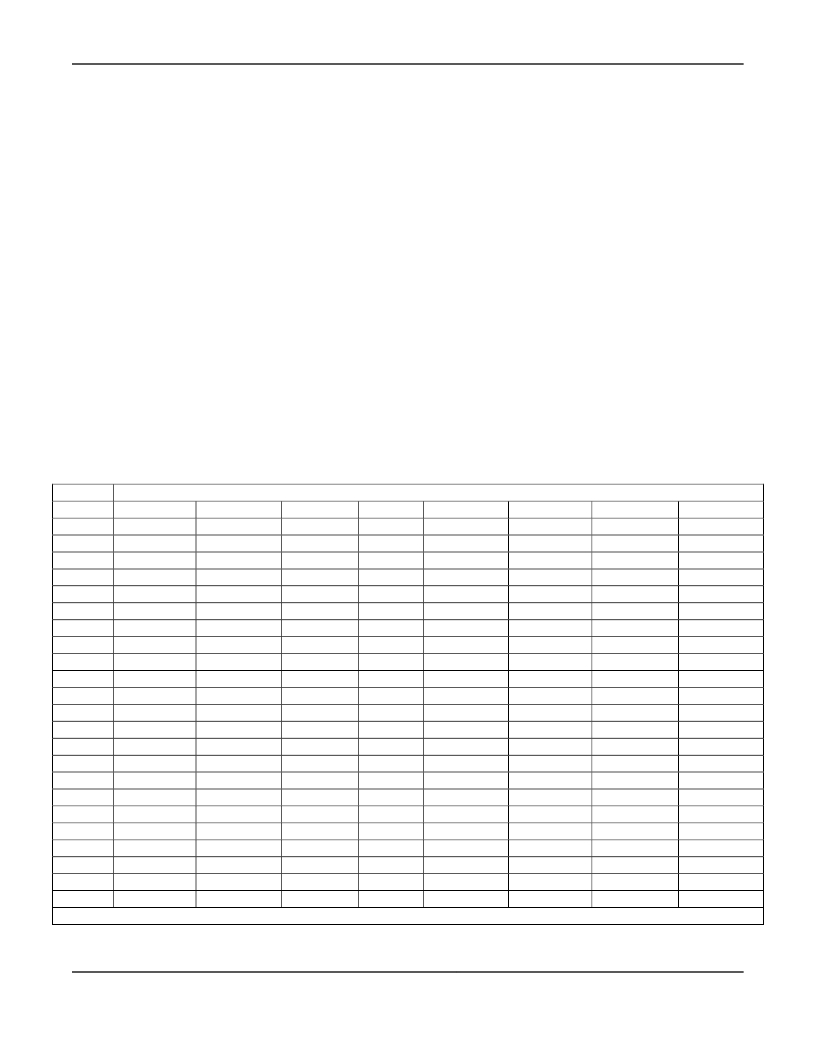

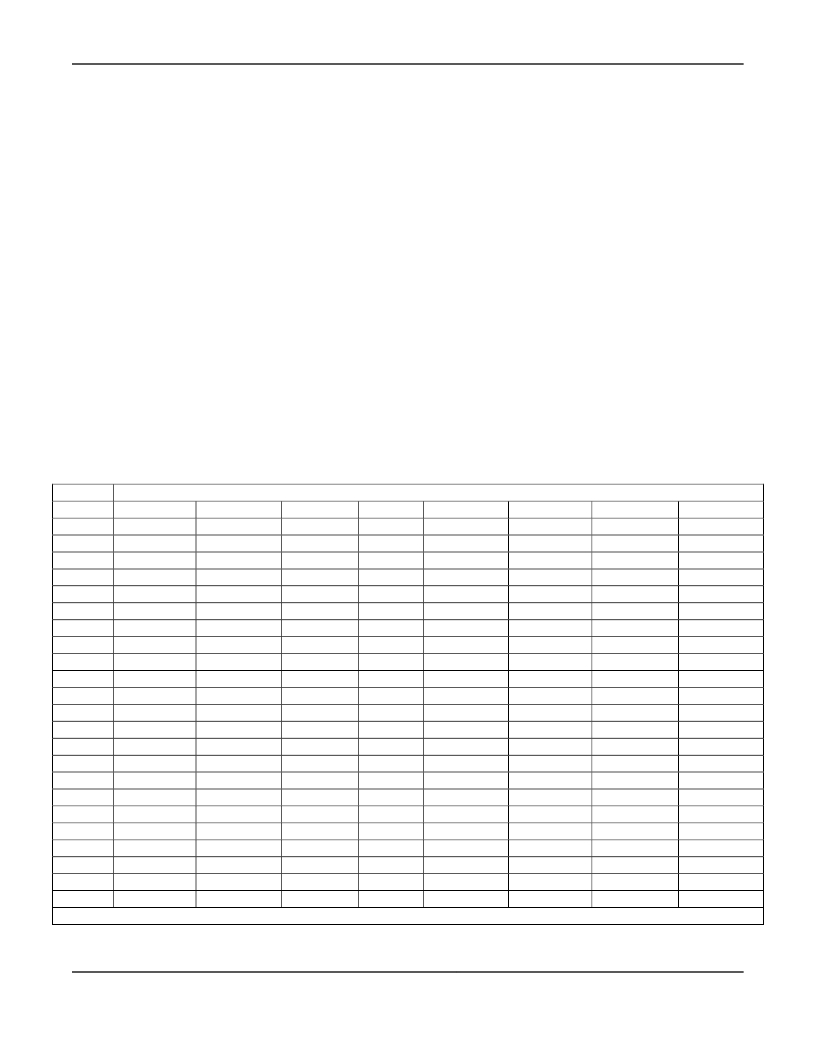

�The� MICRF505� functions� are� enabled� through� a�

�number� of� programming� bits.� The� programming� bits�

�are� organized� as� a� set� of� addressable� control�

�registers,� each� register� holding� 8� bits.�

�There� are� 23� control� registers� in� total� in� the�

�MICRF505,� and� they� have� addresses� ranging� from� 0�

�to� 22.� The� user� can� read� all� the� control� registers.�

�The� user� can� write� to� the� first� 22� registers� (0� to� 21);�

�the� register� 22� is� a� read-only� register.�

�All� control� registers� hold� 8� bits� and� all� 8� bits� must� be�

�written� to� when� accessing� a� control� register,� or� they�

�will� be� read.� Some� of� the� registers� do� not� utilize� all� 8�

�bits.� The� value� of� an� unused� bit� is� “don’t� care.”�

�The� control� register� with� address� 0� is� referred� to� as�

�ControlRegister0,� the� control� register� with� address� 1�

�is� ControlRegister1� and� so� on.� A� summary� of� the�

�control� registers� is� given� in� the� table� below.� In�

�addition� to� the� unused� bits� (marked� with”-“)� there� are�

�a� number� of� mandatory� bits� (marked� with� “0”� or� “1”).�

�Always� maintain� these� as� shown� in� the� table.�

�Adr�

�MICRF505BML/YML�

�The� control� registers� in� MICRF505� are� accessed�

�through� a� 3-wire� interface;� clock,� data� and� chip�

�select.� These� lines� are� referred� to� as� SCLK,� IO,� and�

�CS,� respectively.� This� 3-wire� interface� is� dedicated�

�to� control� register� access� and� is� referred� to� as� the�

�control� interface.� Received� data� (via� RF)� and� data� to�

�transmit� (via� RF)� are� handled� by� the� DataIXO� and�

�DataClk� (if� enabled)� lines;� this� is� referred� to� as� the�

�data� interface.�

�The� SCLK� line� is� applied� externally;� access� to� the�

�control� registers� are� carried� out� at� a� rate� determined�

�by� the� user.� The� MICRF505� will� ignore� transitions� on�

�the� SCLK� line� if� the� CS� line� is� inactive.� The�

�MICRF505� can� be� put� on� a� bus,� sharing� clock� and�

�data� lines� with� other� devices.�

�All� control� registers� should� be� written� to� after� a�

�battery� reset.� During� operation,� it� is� sufficient� to� write�

�to� one� register� only.� The� MICRF505� will�

�automatically� enter� power� down� mode� after� a� battery�

�reset.�

�Data�

�A6…A0�

�0000000�

�0000001�

�0000010�

�0000011�

�0000100�

�0000101�

�0000110�

�0000111�

�0001000�

�0001001�

�0001010�

�0001011�

�0001100�

�0001101�

�0001110�

�0001111�

�0010000�

�0010001�

�0010010�

�0010011�

�0010100�

�0010101�

�0010110�

�D7�

�LNA_by�

�Modulation1�

�CP_HI�

�‘1’�

�Mod_F2�

�-�

�-�

�BitRate_clkS1�

�‘1’�

�‘0’�

�-�

�-�

�N0_7�

�-�

�M0_7�

�-�

�-�

�N1_7�

�-�

�M1_7�

�‘1’�

�-�

�FEE_7�

�D6�

�PA2�

�Modulation0�

�SC_by�

�‘1’�

�Mod_F1�

�-�

�Mod_clkS2�

�BitRate_clkS0�

�‘1’�

�‘0’�

�-�

�-�

�N0_6�

�-�

�M0_6�

�-�

�-�

�N1_6�

�-�

�M1_6�

�‘0’�

�-�

�FEE_6�

�D5�

�PA1�

�‘0’�

�‘0’�

�‘0’�

�Mod_F0�

�‘0’�

�Mod_clkS1�

�RefClk_K5�

�ScClk5�

�‘1’�

�A0_5�

�-�

�N0_5�

�-�

�M0_5�

�A1_5�

�-�

�N1_5�

�-�

�M1_5�

�‘1’�

�-�

�FEE_5�

�D4�

�PA0�

�‘0’�

�PA_By�

�VCO_IB2�

�Mod_I4�

�‘1’�

�Mod_clkS0�

�RefClk_K4�

�ScClk4�

�XCOtune4�

�A0_4�

�-�

�N0_4�

�-�

�M0_4�

�A1_4�

�-�

�N1_4�

�-�

�M1_4�

�‘1’�

�-�

�FEE_4�

�D3�

�Sync_en�

�RSSI_en�

�OUTS3�

�VCO_IB1�

�Mod_I3�

�Mod_A3�

�BitSync_clkS2�

�RefClk_K3�

�ScClk3�

�XCOtune3�

�A0_3�

�N0_11�

�N0_3�

�M0_11�

�M0_3�

�A1_3�

�N1_11�

�N1_3�

�M1_11�

�M1_3�

�‘0’�

�FEEC_3�

�FEE_3�

�D2�

�Mode1�

�LD_en�

�OUTS2�

�VCO_IB0�

�Mod_I2�

�Mod_A2�

�BitSync_clkS1�

�RefClk_K2�

�ScClk2�

�XCOtune2�

�A0_2�

�N0_10�

�N0_2�

�M0_10�

�M0_2�

�A1_2�

�N1_10�

�N1_2�

�M1_10�

�M1_2�

�‘1’�

�FEEC_2�

�FEE_2�

�D1�

�Mode0�

�PF_FC1�

�OUTS1�

�VCO_freq1�

�Mod_I1�

�Mod_A1�

�BitSync_clkS0�

�RefClk_K1�

�ScClk1�

�XCOtune1�

�A0_1�

�N0_9�

�N0_1�

�M0_9�

�M0_1�

�A1_1�

�N1_9�

�N1_1�

�M1_9�

�M1_1�

�‘0’�

�FEEC_1�

�FEE_1�

�D0�

�Load_en�

�PF_FC0�

�OUTS0�

�VCO_freq0�

�Mod_I0�

�Mod_A0�

�BitRate_clkS2�

�RefClk_K0�

�ScClk0�

�XCOtune0�

�A0_0�

�N0_8�

�N0_0�

�M0_8�

�M0_0�

�A1_0�

�N1_8�

�N1_0�

�M1_8�

�M1_0�

�‘1’�

�FEEC_0�

�FEE_0�

�Names� of� programming� bits,� unused� bits� (“-“)� and� mandatory� bits� (“1”� or� “0”)� are� shown.� Change� of� mandatory� bits� may� cause� malfunction� .�

�Table� 1.� Control� Registers� in� MICRF505�

�October� 2006�

�9�

�M9999-103106�

�+1� 408-944-0800�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MICRF506DEV1

EVAL BOARD EXPERIMENTAL MICRF506

MICRF507YML TR

TXRX FSK LOW PWR W/AMP 32MLF

MICRF600DEV1

KIT DEV RADIOWIRE 902-928MHZ

MK01-C

SENSOR REED SPST-NO SMD

MK01-H

SENSOR REED SPDT-CHANGE SMD

MK02/0-1A66-500W

SENSOR REED SPST-NO

MK02/6-0

SENSOR REED PCB 24MM T/H

MK03-1C90C-500W

SENSOR REED SPDT CYLINDER

相关代理商/技术参数

MICRF505DEV1

制造商:Micrel Inc 功能描述:KIT MICRF505 EVALUATION

MICRF505L

制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:850MHz and 950MHz ISM Band Transceiver

MICRF505LYML

制造商:Rochester Electronics LLC 功能描述: 制造商:RF Micro Devices Inc 功能描述:

MICRF505LYML TR

功能描述:射频收发器 850MHz to 950MHz, 2.25V to 5.5V FSK Transceiver with +10dBm Power Amplifier

RoHS:否 制造商:Atmel 频率范围:2322 MHz to 2527 MHz 最大数据速率:2000 Kbps 调制格式:OQPSK 输出功率:4 dBm 类型: 工作电源电压:1.8 V to 3.6 V 最大工作温度:+ 85 C 接口类型:SPI 封装 / 箱体:QFN-32 封装:Tray

MICRF505YML

制造商:Micrel Inc 功能描述:433/915MHZ ITRANSCEIVER SMD MLF32 制造商:Micrel Inc 功能描述:433/915MHZ ITRANSCEIVER, SMD, MLF32 制造商:Micrel Inc 功能描述:433/915MHZ ITRANSCEIVER, SMD, MLF32; Frequency Min:850MHz; Frequency Max:950MHz; Modulation Type:FSK; Sensitivity dBm:-111dBm; Data Rate:200Kbps; Supply Voltage Min:2V; Supply Voltage Max:2.5V; RF IC Case Style:MLF; No. of Pins:32; ;RoHS Compliant: Yes

MICRF505YML TR

功能描述:射频收发器 850MHz to 950MHz, 2.0V to 2.5V FSK Transceiver with +10dBm Power Amplifier

RoHS:否 制造商:Atmel 频率范围:2322 MHz to 2527 MHz 最大数据速率:2000 Kbps 调制格式:OQPSK 输出功率:4 dBm 类型: 工作电源电压:1.8 V to 3.6 V 最大工作温度:+ 85 C 接口类型:SPI 封装 / 箱体:QFN-32 封装:Tray

MICRF505YML-TR

功能描述:IC RF TxRx Only General ISM < 1GHz 850MHz ~ 950MHz 32-VFQFN Exposed Pad, 32-MLF? 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:有效 类型:仅限 TxRx 射频系列/标准:通用 ISM < 1GHz 协议:- 调制:FSK 频率:850MHz ~ 950MHz 数据速率(最大值):200kbps 功率 - 输出:10dBm 灵敏度:-111dBm 存储容量:- 串行接口:SPI GPIO:- 电压 - 电源:2 V ~ 2.5 V 电流 - 接收:8.6mA ~ 13.5mA 电流 - 传输:14mA ~ 28mA 工作温度:-40°C ~ 85°C 封装/外壳:32-VFQFN 裸露焊盘,32-MLF? 标准包装:1

MICRF506

制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:410MHz and 450MHz ISM Band Transceiver